而不是对输入 PWM 暗IM体育官网登录入口APP下载:号作出反应

本想象攻略分为三小我,将批注何如为电力电子运用中的功率开关器材采用得当的阻隔

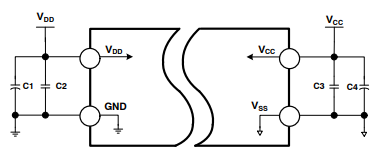

以下是运用分开式栅极驱动器电源时应细心的很少建议。VDD和 VCC的旁途电容抵挡完成实在的距离式栅极驱动器功能至关慌乱。

建议采选具有妥善电压额外值、温度系数和电容容差的低 ESR 和低 ESL 外观贴装多层陶瓷电容 (MLCC)。栅极驱动器的输出偏置电源引脚必要旁途电容,其值至少应为开合器材栅极电容的 10 倍,何况不小于 100 nF;此电容应坐落尽能够迫临该器材的场合,以用于解耦。创议操作 2 个电容:一个 100 nF 陶瓷表面贴装电容和一个并联的几微法电容,如图 1 所示。

相同,输入侧的 VDD和 GND 引脚之间也应组织一个旁道电容。忖量到输入侧的逻辑电道会花费少数电流,此旁途电容的最小提议值为 100 nF。

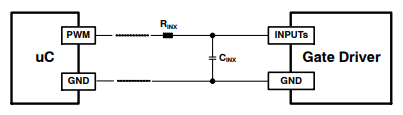

为了赢得杰出的暗号资料和抗扰度,或许在微约束器和栅极驱动器输入之间安置一个输入滤波器 RC 收集,如图 2 所示。

● 具有较短延宕期间的 RC 滤波器与栅极驱动器自己集成的谨慎滤波器的组闭。

● 由最大 100 pF 电容和最多 100Ω 电阻构成的小容性滤波器可治服驱动器输入端的高频噪声。滤波器电容克服共模噪声。

● 滤波器电阻有助于回护操控器。串联电阻会约束接地反弹时刻流入流出操控器的电流,委曲栅极驱动线的寄生电感(它或许导致振铃),并有助于制服任何由长输入走线吸取的 EMI。

● 此 RC 滤波器需要放在尽可能接近栅极驱动器引脚引线的当地。高压输出电途的共模瞬变噪声恐怕会打搅低压输入侧。数字约束输入应运用低阻抗暗号源以防卫闪现毛刺或形成意外开合。

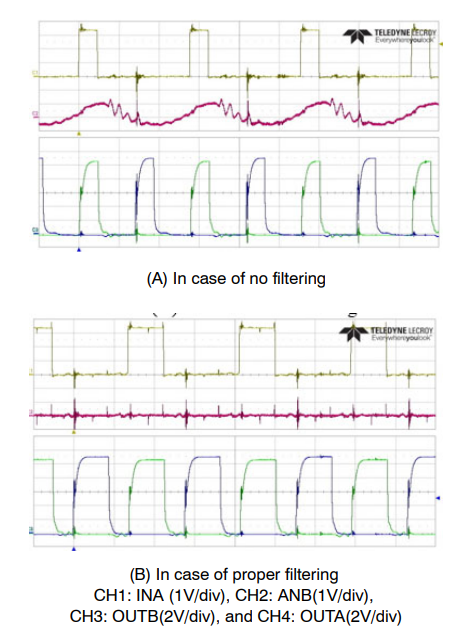

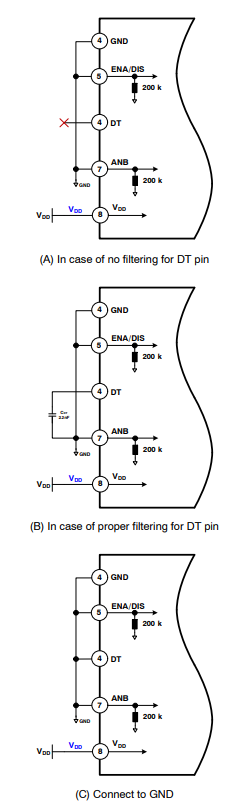

其我们输入引脚(如 ANB、DT 和 ENA/DIS)也必要妥善滤波,以使编制正经。因为功率级瞬变电压和电流的电磁滋扰 (EMI),输入滤波不当大约导致各式不良效果。

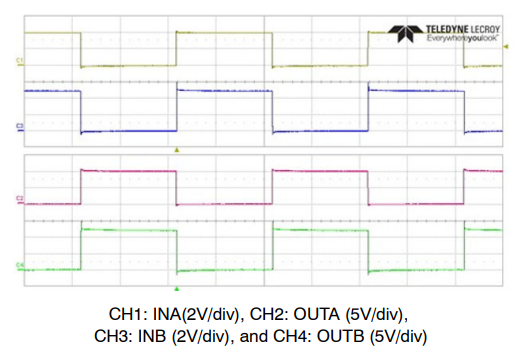

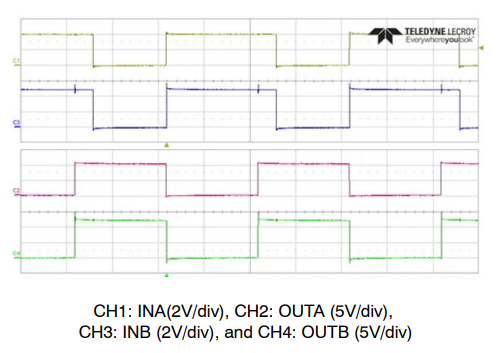

譬喻,图 3 映现了 ANB 引脚浮空时的作业波形,上方图片没有滤波,下方图片则运用了妥善滤波。如试验成果所示,在没有旁途电容的境况下敬重到噪声暗记,而当迫临此引脚运用 1 nF 以上的旁路电容时,噪声暗记消灭。

驱动器引脚的噪声可能会耦闭到输入引脚(ANB 和 ENA/DIS)上,导致驱动器对瞬变作出呼应,而不是对输入 PWM 暗号作出呼应。这大约会变成驱动器输入和输出显现不良动作,何况大约会颓唐编制机能。

其它,倘若驱动器的 ANB 和 ENA/DIS 引脚之间的阻隔较长,那么必要特别详明驱动器的布局和滤波,以防止这种不良举动。

当运用约束器驱动几英寸或更长间隔外的 ENA/DIS 引脚时,需要将低 ESR/ESL 的 1 nF 电容放置在引脚左近。

在需要快快禁用响合时刻的境况下,应使约束器更迫近驱动器,行使高驱动强度输出,并最大水平地省掉栅极驱动环路中的杂散电感。

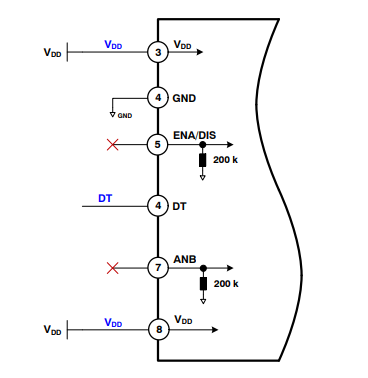

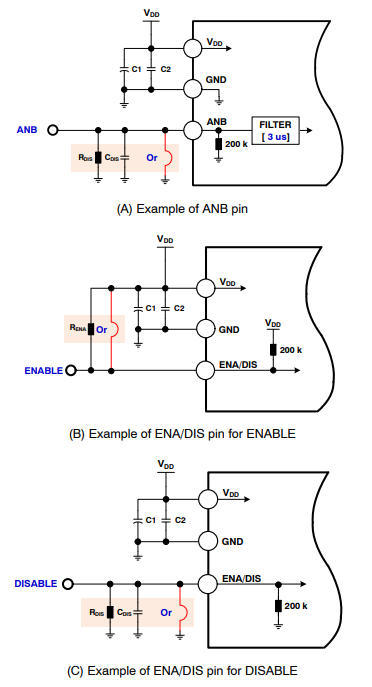

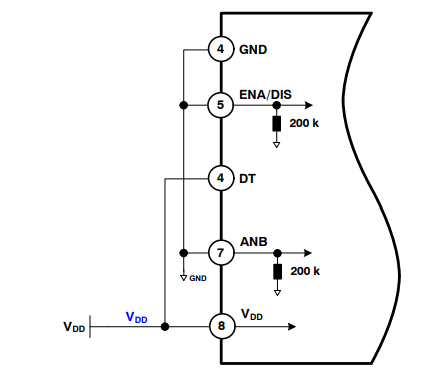

ANB 引脚:要是不运用 ANB 引脚,应将其直连 GND 引脚,或运用 1 nF 电容。若是无法将 ANB 引脚联合到 GND,那么发起运用数十 kΩ(如 10 kΩ ~ 47 kΩ)的外手下拉电阻,以当心外部打扰导致 ANB 功效意外激活(即便其内中有 3.3μs 滤波器),如图 5 (A) 所示。

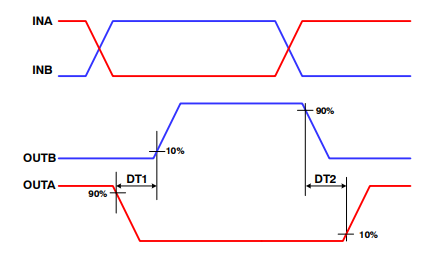

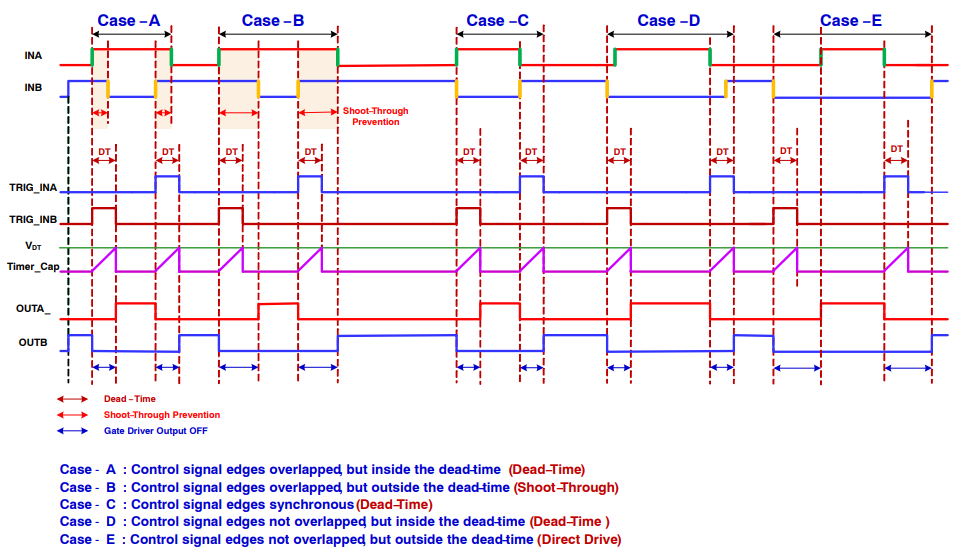

只需两个外部输入暗号的死区时刻(INA 和 INB 暗号之间)比内部制作的死区年月(DT1 和 DT2)短,编制就会自动刺进死区时刻。不然,假若外部输入暗号死区时刻大于内中死区年月,则栅极驱动器不会编削死区功夫。内部死区期间界说如图 6 所示。

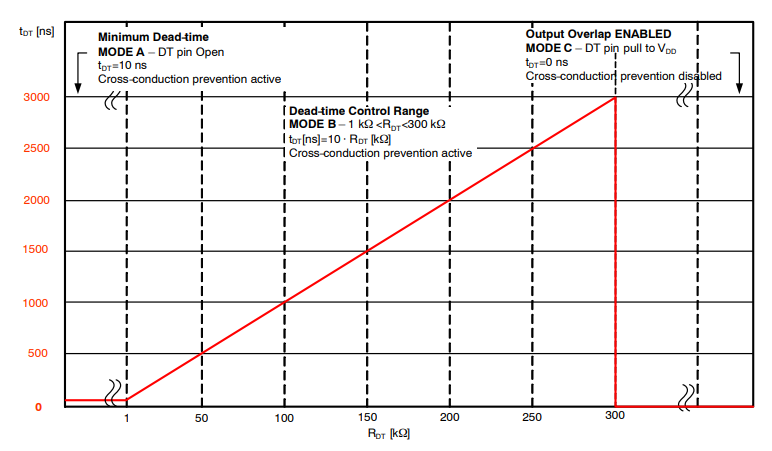

在形式 A 下,当 DT 引脚开道时,最小死区时刻 (tDTMIN) 典型值为 10 ns,不许愿驱动器两个输出(OUTA 和 OUTB)之间交错导通。在形式 B下,当 DT 引脚电阻在 1 k 和 300 k 之间时,外部电阻 (RDT) 操控死区功夫。

两道输出之间的死区时刻 (DT) 依据下式征战:DT(单位为 ns)= 10 × RDT(单位为 kΩ)。

在形式 C下,当 DT 引脚被拉至 VDD时,承诺两个输出重迭,如图 8 所示。

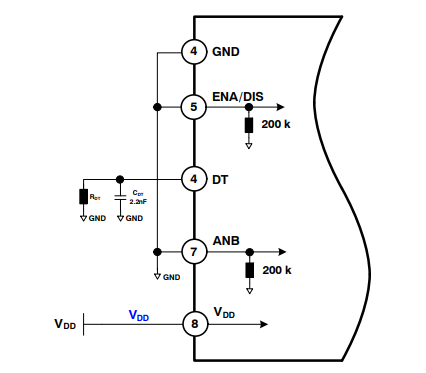

当 DT 引脚浮空时,首倡将 DT 引脚直连 GND 引脚,或操作 2.2 nF 电容,辨别如图 9 的中心和下方图形所示。

如图 10 所示,当 DT 引脚浮空时,最小死区时分 (tDTMIN) 典范值为 10 ns,不应承驱动器两个输出(OUTA 和 OUTB)之间交错导通。

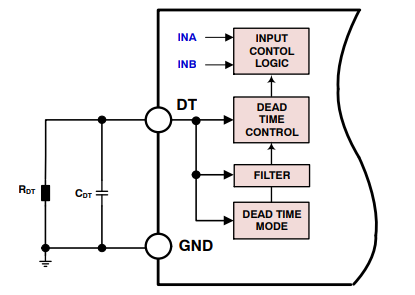

假若原委死区时刻约束电阻对死区时刻举行编程,应并联方案一个值大于 2.2nF 的电容,以进步速快开关瞬变功夫的抗扰度,如图 11 所示。

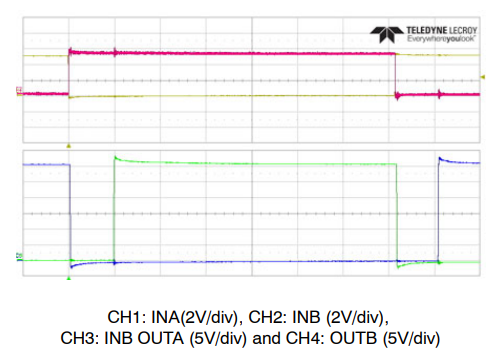

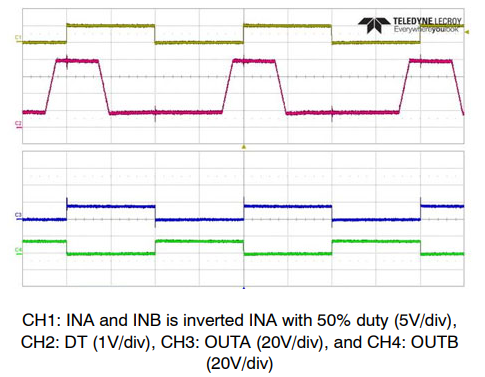

当 DT 引脚电阻在 1 kΩ 和 300 kΩ 之间时,外部电阻 (RDT) 约束死区时期。图 12 闪现了 DT 引脚具有 100 kΩ 电阻时的实践功劳。

倘若无需死区年月,应将死区功夫引脚贯串到 VDD以停用 DT 电途,如图 13 所示,实施收成如图 14 所示。

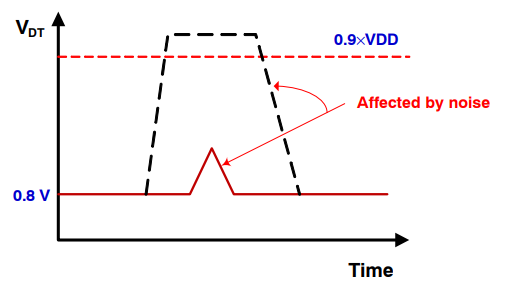

当 DT 引脚浮空时,在浪涌试验时刻(如雷击浪涌)DT 引脚上或许有反常噪声。纵然 DT 引脚里边关于开途和近距离检测分辩有 3μs 和 2μs 的滤波期间,但倘若 DT 引脚电压受噪声旗帜教养而高出额外电压电平,死区时分操控形式仍会变为形式 C,来由死区功夫极限形式改动取决于 DT 引脚电压。

例如,倘若 DT 引脚电压低于 0.9 × VDD,则当 DT 引脚浮空时,死区时刻具有最小值(榜样值 10 ns),DT 引脚的稳态电压约为 0.8 V。

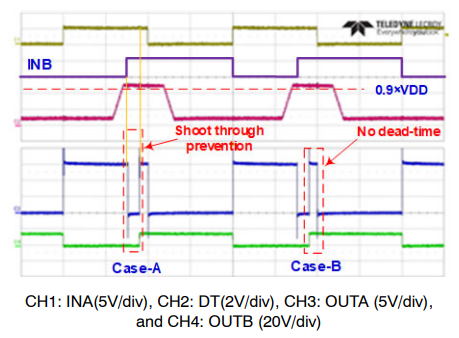

倘若噪声导致 DT 引脚电压赶过 0.9 × VDD 且一向 3μs 以上,死区时辰约束形式会被禁用,这意味着两个通途之间没有死区年月,如图 15 所示。

所以,倡议为 RDT 添补一个 2.2nF 或以上的陶瓷电容 (CDT),并使其迫临芯片,以结束更好的抗扰度和两个通途之间更好的死区时分成家,如图 16 所示。

首要考量是进程 RDT 的电流用于兴办死区时辰,此电流跟着 RDT 值的增大而减小。

试验收效闪现,关于 5 V 境遇的 VDD,当 DT 引脚浮空且外部施加的电压低于 0.9 × VDD 时,死区年月极限形式安稳,即仍为形式 A,如图 17 所示。

图 17. DT 引脚浮空且外部施加的电压低于 0.9 × VDD 时的实施波形

不过,对待 5 V 境遇的 VDD,当 DT 引脚浮空且外部施加的电压高于 0.9 × VDD并连续 3μs 以上时,死区时期形式从形式 A 变为形式 C,比如图 18 中的环境 B 所示。如境遇 A 所示,针对 DT 引脚开路检测,其里边有 3μs 滤波年月,是以死区时分约束形式并未替换,防备击穿效能仍在运转。

图 18. DT 引脚浮空且外部施加的电压高于 0.9 × VDD时的履行波形

本文由:IM体育提供 上一篇:Im体育app官方下载入口:履历自研AutoSar 下一篇:IM体育官网app下载手机端:为了抵消这种传染